Триггер представляет собой элементарный цифровой автомат. Он имеет два состояния устойчивости. Одному из них присваивается значение «1», а другому — «0».

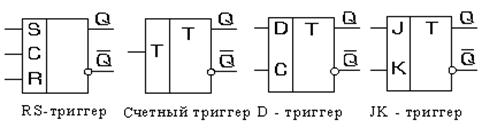

По способу реализации логических связей различают следующие виды упомянутых устройств: JK-триггер, RS-триггер, T-триггер, D-триггер и т. д.

Предметом нашего сегодняшнего разговора являются автоматы типа JK. Они отличаются от RS-приборов тем, что при подаче на вход информации, запрещенной для RS-триггеров, инвертируют хранимые в них сведения.

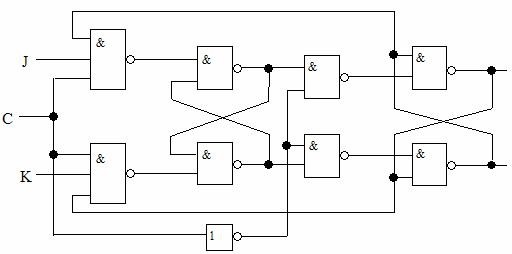

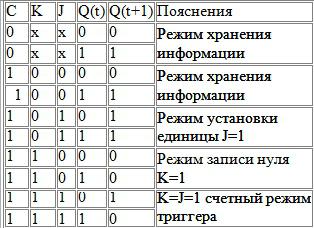

Представляем вашему вниманию таблицу переходов, которая описывает работу JK-триггера. При минимизации каты Карно выводится характеристическое уравнение для рассматриваемого устройства: Q(t+1)=K’t Qt V Jt Q’t.

Из таблицы видно, что состояние прибора определяется не только значениями информации на входах J и K, но и состоянием на выходе Qt, которое ранее определяло JK-триггер. Это позволяет строить функциональные схемы таких устройств на двухступенчатых автоматах типа RS. JK-приборы бывают синхронными и асинхронными.

Для проектирования JK-триггера из двухступенчатого устройства RS синхронного типа требуется соединить обратные связи выходов двухступенчатого автомата RS со входами логических элементов его первой ступени.

Принцип работы JK-триггера: если на информационных (J и K) входах устройства подан уровень нуля, то на выходе элементов И-НЕ (1 и 2) устанавливается уровень единицы, и JK-триггер сохранит свое состояние. Например, Q будет равен логическому нулю, Q’ — логической единице. В таком случае при подаче сигналов J и C, равных логической единице, на входе элемента И-НЕ1 устанавливается логический нуль и, соответственно, уровень логической единицы на входе первого T-триггера. При снятии синхронизирующего сигнала (С равен нулю) состояние упомянутого устройства Т-типа уровнем логического нуля с выхода И=НЕ3 передастся на вход второго T-триггера. В результате JK-триггер переключится в состояние логической единицы (в таком случае Q равен единице, а Q’ равен нулю). Теперь, если на входе триггера (К и С) подается сигнал, равный логической единице, то на выходе элемента И-НЕ2 логический нуль установит первый Т-триггер в состояние нуля. После снятия синхронизирующего сигнала с выхода элемента И-НЕ4 логический нуль передастся на вход второго автомата типа Т, и JK-триггер переключается в состояние логического нуля.

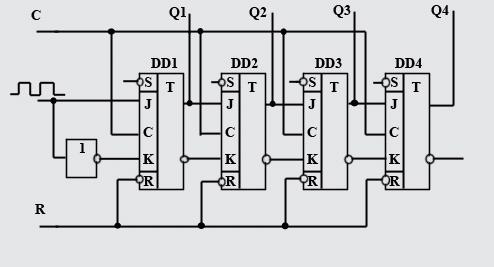

При проектировании сложных логических схем необходимы приборы разных типов. Поэтому выгоднее изготовить универсальный тип устройства, которое можно использовать в различных режимах работы и модификациях. В интегральной схемотехнике наибольшее распространение получили синхронные D- и JK-триггеры. В электронно-вычислительных машинах широко используют цифровые автоматы JK типа с групповыми J, K и дополнительными установочными R, S-входами. Каждая группа объединена конъюнкцией, что позволяет расширить логические возможности и JK-триггера.

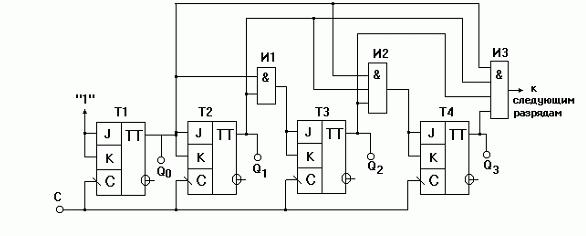

Автоматические устройства такого типа удобно использовать при конструировании счетчиков (узел ЭВМ, который осуществляет счет и хранение кода числа подсчитанных сигналов). Например, на фото показан счетчик на JK-триггерах. Структурная организация двоичных счетчиков с параллельным переносом значительно упрощается, если их строить на приборах типа JK со встроенными логическими элементами И.

Также такие триггеры нашли применение при конструировании сдвигающих регистров.

Регистры сдвига – это узлы, выполняющие смещение двоичной информации вправо и влево по регистру в зависимости от управляющих сигналов.

Устройство и принцип работы JK-триггера

Наиболее сложный по конструкции триггер широко используется в цифровой технике благодаря своей универсальности. Это, так называемый, JK-триггер.

На рисунке видно, что JK-триггер имеет пять входов, в том числе прямой Q и инверсный выходы Q.

К уже известным входам R (Reset) – сброс, S (Set) – установка, С — тактовый вход добавлены ещё два. Это входы J (Jump) и K (Kill).

Благодаря наличию этих дополнительных входов появляется возможность несложными схемными средствами достигать интересных результатов.

Логика работы основных входов (C, J, K) реализована следующим образом. Если на входе J высокий потенциал, а на входе K – ноль, то триггер установится в единичное состояние по спаду тактового импульса на входе С. Если на входе J – ноль, а на входе К высокий потенциал то по спаду тактового импульса триггер "сбросится" в нулевое состояние. Когда J=K=0 независимо от тактовых импульсов состояние триггера не меняется. И если J=K=1, то при приходе каждого тактового импульса состояние триггера меняется на противоположное. В этом случае триггер работает как делитель частоты на два.

Благодаря такой логике работы появляется возможность довольно гибко настраивать алгоритм работы триггера. Такая универсальность позволяет использовать JK-триггер в устройствах со сложной логикой работы.

На JK-триггерах несложно реализовать делитель частоты на десять. Если мы подадим на вход импульсы с частотой 10 кГц, то на выходе получим уже 1 кГц. Такие схемы называют декадным делителем или декадой.

Делители с различным коэффициентом пересчёта раньше активно использовались радиолюбителями при изготовлении электронных часов и несложных музыкальных инструментов. Данная схема очень неэкономична и займёт много места, если собирать её на дискретных элементах, так как в ней используется четыре триггера и элемент 2И.

В широко распространённую серию К155 на базе ТТЛ логики входит универсальный JK-триггер К155ТВ1 (КМ155ТВ1). Зарубежными аналогами этой микросхемы являются SN7472N, 7472, SN7472J. Этот триггер построен по двухступенчатой схеме и имеет сложную входную логику, где три входа J и три входа K объединены по схеме логического И. Кроме того триггер имеет прямой и инверсный выходы, входы установки и сброса (S и R) и вход тактовых импульсов С. Вот так он обозначается на схеме.

Вот так выглядит его внутренняя структура. Те, кто знаком с базовыми логическими элементами и устройством простейшего RS-триггера разберутся в устройстве JK-триггера без особых трудностей.

Этот триггер, как видно на схеме, организован на основе логических элементов И – НЕ с различным числом входов. В схеме присутствуют элементы: 2И – НЕ, 3И – НЕ, и 6И – НЕ. Наличие элементов 6И – НЕ, а также двухступенчатой структуры делает триггер многоцелевым и универсальным. В зависимости от конечной задачи, входы триггера могут объединяться или подключаться к другим логическим элементам схемы.

На микросхеме К155ТВ1 можно собрать несложную схему наглядно демонстрирующую работу JK-триггера. Как у почти всех микросхем этой серии 7 вывод — это корпус, а 14 вывод — это напряжение питания +5V . На 12 вывод (вход тактовых импульсов), и на прямой и инверсный выходы триггера, (выводы 8 и 6), необходимо подключить светодиоды через токоограничивающие резисторы.

После подключения питания один из выходных светодиодов загорается. Теперь можно проверить работу триггера по входам установки и сброса. Для этого необходимо поочерёдно подавать на выводы 2 (R) и 13 (S) низкий потенциал или "корпус".

Светодиодные индикаторы будут попеременно загораться и гаснуть, индицируя в каком состоянии находится триггер. Это проверка работоспособности. Теперь можно посмотреть работу триггера в счётном режиме. Для этого можно объединить входы J и K и соединить их с напряжением питания +5V через резистор.

Этого можно и не делать. По определению любой вывод микросхемы ТТЛ-логики, если он просто "висит" в воздухе и никуда не подключен, находится под высоким потенциалом (уровень логической единицы). Соединение свободных выводов микросхем с плюсом источника питания производится для предотвращения случайных срабатываний, то есть для повышения помехозащищённости.

Теперь можно подать на вход С импульсы такой частоты, чтобы их было визуально видно по работе светодиода HL1. Светодиоды, подключенные к выходам триггера, будут срабатывать с частотой в два раза меньше. То есть в этом режиме JK-триггер делит частоту входного сигнала на два.

Для тестирования триггера понадобится источник внешнего тактового сигнала, чтобы подать последовательность импульсов на вход C.

Простейший генератор прямоугольных импульсов можно собрать, используя микросхему К155ЛА3.

Она содержит четыре элемент 2И – НЕ. Для генератора достаточно двух элементов. Период следования импульсов можно ориентировочно рассчитать по формуле T=1,4*R1*C1. Частота генератора прямоугольных импульсов в таком случае приблизительно будет равна f = 1/T. Для тех номиналов резистора R1 и конденсатора C1, что показаны на схеме, период генератора ориентировочно равен: T = 1,4 * 1000 * 0,00047 = 0,658 (с). Частота f = 1/0,658 = 1,5197.

1,5 (Гц). В дальнейшем этот простейший генератор можно использовать для проверки работоспособности различных цифровых устройств.

В цифровых автоматах значение функции зависит не только от значения переменных в данный момент времени (данный такт), но и от их последовательности в предыдущие моменты (такты). Поэтому раздел алгебры логики, описывающий работу цифровых автоматов, обладающих памятью, называется последовательностной логикой. Основным элементом последовательностной логики является триггерный элемент или просто триггер.

Триггером называется устройство, обладающее двумя состояниями устойчивого равновесия и способное под воздействием внешнего управляющего сигнала переходить скачком из одного состояния в другое.

Основные области применения триггера:

запоминающая ячейка в устройствах электронной памяти ЭВМ;

элемент деления на 2 в импульсных счетчиках и делителях частоты;

устройство для расширения (увеличения длительности) импульсов;

устройство, восстанавливающее форму прямоугольного импульса.

Классификация триггеров по способу организации логических связей:

триггеры с раздельным запуском или триггеры с установочными входами – RS-триггеры;

триггеры со счетным входом Т-триггеры;

Триггеры с приемом информации по одному входу – D-триггеры;

Универсальные триггеры – JK-триггеры.

По способу записи информации триггеры делят на асинхронные и синхронизируемые (тактируемые). В асинхронных триггерах информация, записанная в триггер, может изменяться в любой момент времени при изменении входных сигналов. В синхронизируемых триггерах информация на выходе может меняться только в определенные моменты времени, задаваемые дополнительным синхронизирующим сигналом.

Как правило, триггер имеет два выхода: прямой Q и инверсный  Состояние триггера определяется по прямому выходу Q. Число входов зависит от выполняемых функций:

Состояние триггера определяется по прямому выходу Q. Число входов зависит от выполняемых функций:

S – вход установки триггера в единичное состояние;

R – вход установки триггера в нулевое состояние;

Т – счетный вход;

D – вход приема информации;

С – вход синхронизации;

J,K – логические входы;

V – вход разрешения / запрета работы триггера.

Условные обозначения триггеров приведены на рис.4.1.

Рис.4.1. 6. Условные обозначения триггеров

Рис.4.2. . Схема асинхронного RS-триггера и его условное

обозначение (кружки у входов указывают на инверсные входы

– управление сигналом логического 0)

В основе всех схем триггеров лежит основной (базовый триггер защелка ) асинхронный RS-триггер. RS-триггер может быть построен на двух логических элементах И-НЕ (рис.4.2) (или ИЛИ-НЕ).

Элементы охвачены цепями обратных связей, для чего выход каждого элемента подключен к одному из входов другого элемента.

Триггер имеет два входа: S – вход установки в единичное состояние (от англ. set – установка) и R – вход сброса в нулевое состояние (от англ. reset – сброс). Логика элементов И-НЕ, на которых построен триггер имеет простое словесное выражение: любой ноль на входе дает единицу на выходе. Из этого следует, что управляющими сигналами для этого триггера будут сигналы логического 0.

При подаче нуля на вход S и единицы на вход R (S=0, R=1) на прямом выходе будет уровень логической 1. Эта единица по цепи обратной связи поступает на один из входов нижнего по схеме элемента и вместе с единицей на входе R дает логический 0 на инверсном выходе. Это режим установки триггера в единичное состояние.

При входных сигналах S=1 и R=0 триггер будет установлен в нулевое состояние: на прямом выходе уровень логического 0, на инверсном – 1.

При подаче на оба входа нулевых сигналов на обоих выходах триггера появится уровень логической 1. Это запрещенный режим. Нельзя одновременно подавать сигналы на установку триггера в нулевое и единичное состояние.

В случае, если S=1 и R=1, то триггер не изменяет своего состояния. В этом можно убедиться, предполагая последовательно, что триггер находился в нулевом или единичном состоянии. Полная таблица истинности RS-триггера приведена в табл. 4.1.

| S | R |  |

|

|

Уравнения, описывающие эту таблицу для  и

и  после их упрощения (способы написания таких уравнений описаны ниже в разделе «Синтез цифровых схем») имеют вид:

после их упрощения (способы написания таких уравнений описаны ниже в разделе «Синтез цифровых схем») имеют вид:

и

и  . Здесь

. Здесь  — состояние триггера до подачи управляющих сигналов,

— состояние триггера до подачи управляющих сигналов,  — состояние триггера после подачи управляющих сигналов.

— состояние триггера после подачи управляющих сигналов.

При S=0 и R=0

при S=0 и R=1

при S=1 и R=0

при S=1 и R=1

Рис.4.3. 3 8. Схема синхронного RS-триггера на элементах И-НЕ

В синхронном RS-триггере (рис. 4.3 8) использованы 4 логических элемента И-НЕ.

Вход С – вход синхронизации. Переключение триггера под действием входных сигналов S и R возможно только при наличии синхронизирующего импульса, т.е. при С=1. При таком (единичном) сигнале на входе С входные элементы И-НЕ по другому входу выполняют функцию НЕ, т.е. этот триггер по входам S и R управляется единичными сигналами. При С=0 на выходах входных элементов будут уровни логической 1, что для следующего за входными элементами простого RS-триггера (см. табл.4.1) определяет режим хранения, т.е. триггер хранит свое предыдущее состояние и не переключается.

При С=1, S=0 и R=0 на выходах входных элементов уровни логической 1 – триггер находится в режиме хранения (см. рис.4.4).

При С=1, S=0 и R=1 на прямом выходе появится логический 0, на инверсном – 1. Это режим установки триггера в нулевое состояние.

Рис.4.4. 9. Распределение сигналов в синхронном RS-триггере при

разных комбинациях сигналов на входах R и S (при С=1)

При С=1, S=1 и R=0 на прямом выходе логическая 1, на инверсном – 0. Это режим установки триггера в единичное состояние.

При С=1, S=1 и R=1 на обоих выходах уровень логической 1 – запрещенный режим. Запрещено одновременно подавать сигналы на установку триггера в единичное и нулевое состояние.

Уравнения для синхронного RS-триггера:

Подставляя в уравнения разные значения С, S, R и Qt , получаем результаты, совпадающие с данными, полученными при анализе схемы.

D-триггер (рис. 4.5 10) имеет в своем составе 4 логических элемента И-НЕ, два из которых образуют простой RS-триггер, а входные подключены к клеммам D (вход приема информации) и С (вход синхронизации). При С=0, как и в синхронном триггере, на выходах входных элементов установятся уровни логической 1. Для выходного RS-триггера это режим хранения.

Рис. 4.5 10. Схема D-триггера на логических элементах И-НЕ

Независимо от состояния входа D на выходе информация не меняется (Qt+1=Qt). При С=1 информация со входа D переписывается на выход Q (Q t+1 = D t). Проследить за состояниями сигналов во всех точках схемы D-триггера при D=0 и D=1 можно по рис. 11.

Рис.4.6 11. Распределение сигналов в D-триггере при D=0 (слева) и

D=1 (справа)

В Т-триггере, при каждом импульсе на входе Т, триггер переключается в противоположное состояние. Т-триггер может быть построен на основе D-триггера при соединении инверсного выхода  со входом D. Вход С D-триггера становится входом Т Т-триггера. Т-триггер может быть построен также на основе синхронного RS-триггера соединением входа R с прямым выходом Q, а входа S с инверсным выходом

со входом D. Вход С D-триггера становится входом Т Т-триггера. Т-триггер может быть построен также на основе синхронного RS-триггера соединением входа R с прямым выходом Q, а входа S с инверсным выходом  (рис.4.7 12).

(рис.4.7 12).

Принцип работы Т-триггера иллюстрируется диаграммами напряжений на рис. 13.

Рис.4.7 12. Варианты реализации Т-триггера

Рис.4.8 13. Диаграммы напряжений для Т-триггера, построенного на

основе D-триггера (слева) и синхронного RS-триггера (справа)

Для реализации Т-триггера необходимо использовать не простые (статические) D или RS-триггеры, описанные выше и срабатывающие по единичному уровню на входе С, а динамические триггеры, срабатывающие по фронту сигнала на входе С. Тогда для схемы Т-триггера на основе D-триггера к моменту прихода первого фронта на входе С, на входе D был уровень логической 1. Эта единица и переписывается на выход Q согласно логике D-триггера. На инверсном выходе появится логический 0. К приходу второго фронта входного сигнала (С) на входе D был уровень логического 0. Он и перепишется на выход Q. Эти процессы записи информации со входа D на выход Q показаны на рис. 4.8 стрелками. Для Т- триггера на основе синхронного RS-триггера процессы аналогичны и основаны на логике синхронного RS-триггера. К моменту прихода первого фронта сигнала на вход С, на входе R был уровень логического 0, а на входе S – уровень логической 1. Триггер установится в единичное состояние. При следующем такте (фронте на входе С) входы R и S обменяются состояниями, на выходе Q появится уровень логического 0.

Таким образом, при каждом входном импульсе Т-триггер переключается в противоположное состояние. Если сравнить периоды входного и выходного сигналов, то можно заметить, что период выходного сигнала в 2 раза больше входного. Т.е. Т-триггер является делителем частоты на 2 и используется в схемах деления частоты и в цифровых счетчиках.

Триггер Шмидта применяется для формирования входного сигнала произвольной формы в сигналы, принимающие два стандартных уровня ”0” и “1”. Варианты схем таких формирователей показаны на рис. 4.9

На рис. 4.9, а показана схема триггера Шмитта, в которой применены два инвертора, входящие в серию логических транзисторно-транзисторных интегральных схем. Положительная обратная связь между инверторами обеспечивается за счет резистора R1, включенного в общую цепь питания элементов. Для увеличения влияния цепи обратной связи, ток через второй инвертор увеличен путем включения дополнительного резистора R2 между выходом Э2 и источником питания. Подобный формирователь на интегральных схемах серии К1533 удовлетворительно работает до частоты несколько мегагерц при подаче на вход синусоидального напряжения амплитудой 0,5 — 0,8 В.

В триггерах Шмитта положительную обратную связь можно ввести также путем включения резистора между выходом второго инвертора и входом первого (рис. 4.6, б). Входное напряжение в этом формирователе подается через дополнительный резистор R1, сопротивление которого также влияет на глубину положительной обратной связи. Увеличение сопротивления этого резистора увеличивает коэффициент положительной обратной связи и уменьшает чувствительность формирователя к входному напряжению.

Вопросы по теме

1. Классификация триггеров простейший триггер защелка RS-триггеры